[bsp][stm32] 移除mini system BSP

Showing

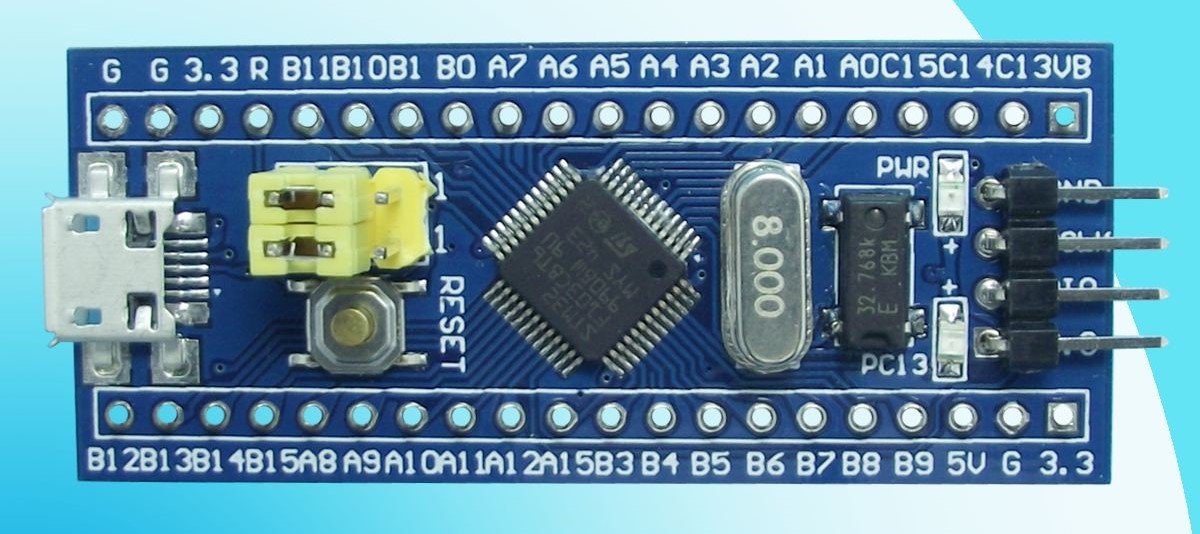

184.1 KB

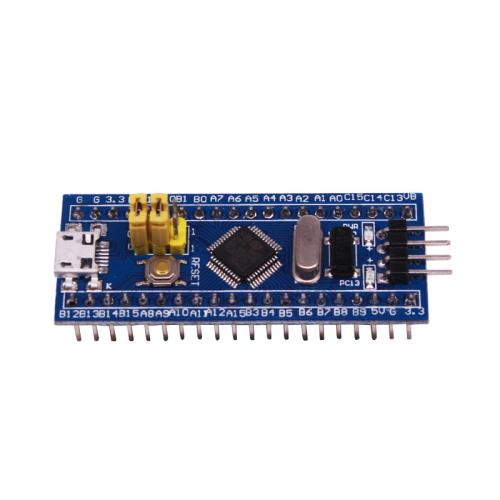

21.7 KB

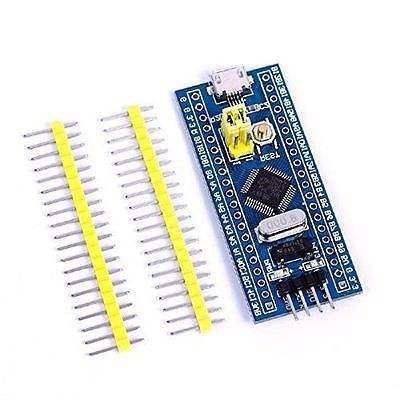

22.7 KB

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

184.1 KB

21.7 KB

22.7 KB