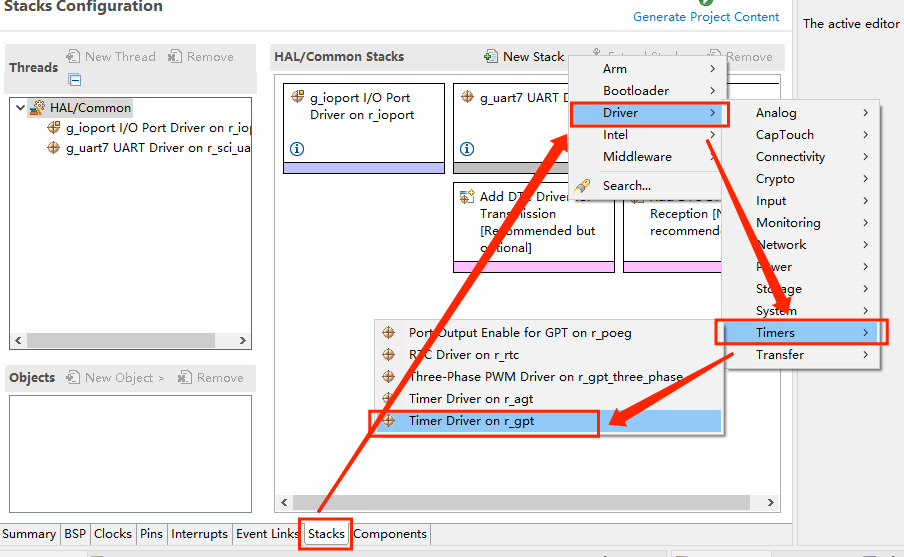

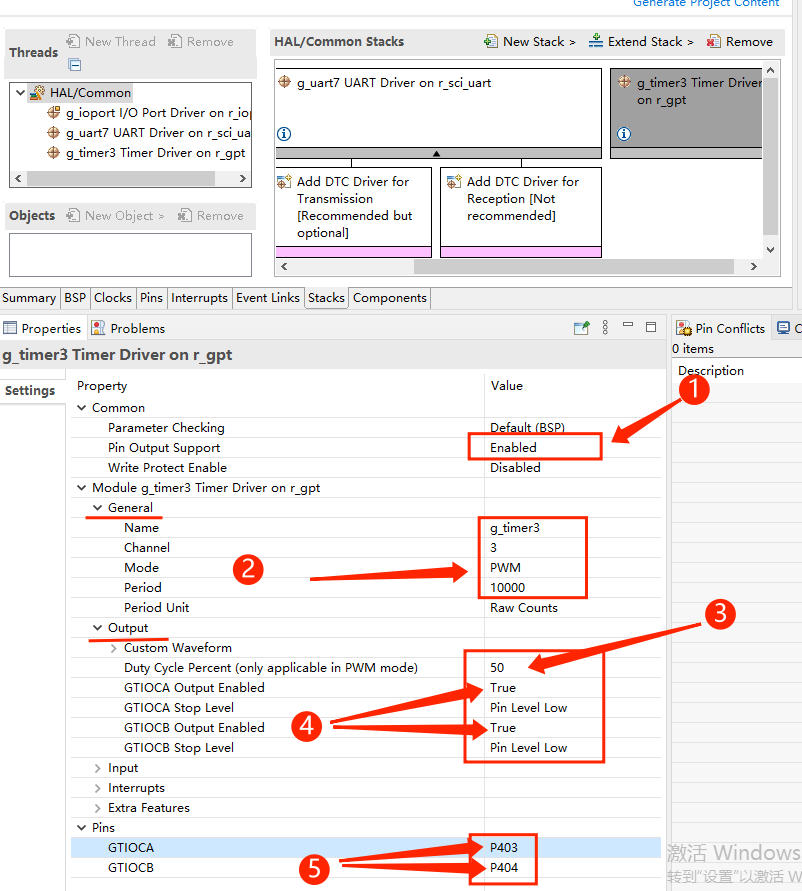

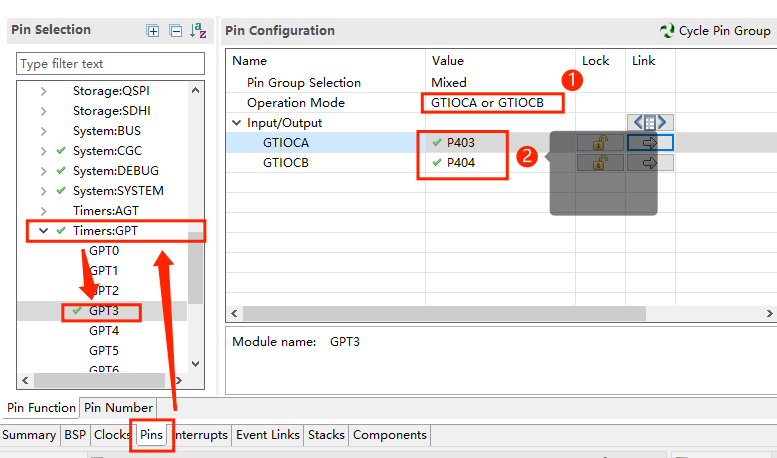

[add] 添加 PWM 驱动

[fix] 修复scons脚本中错误的依赖宏

Showing

58.2 KB

78.7 KB

35.7 KB

bsp/ra6m4-cpk/drivers/drv_pwm.c

0 → 100644

bsp/ra6m4-cpk/drivers/drv_pwm.h

0 → 100644

[fix] 修复scons脚本中错误的依赖宏

58.2 KB

78.7 KB

35.7 KB