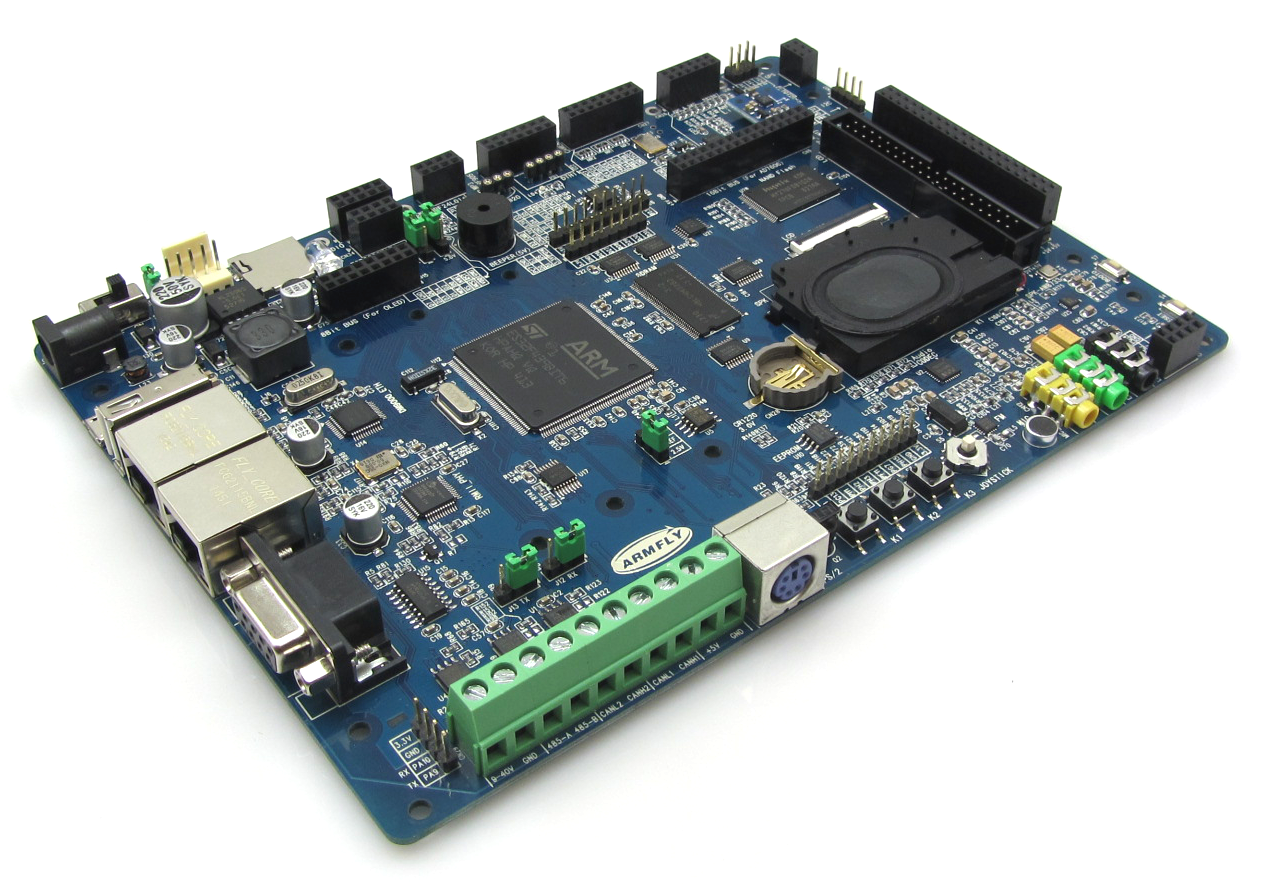

[bsp][stm32] add stm32f429-armfly-v6 bsp

Showing

此差异已折叠。

此差异已折叠。

1.2 MB

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。