Merge branch 'master' into mutexrevert

Showing

bsp/ft2004/.config

0 → 100644

此差异已折叠。

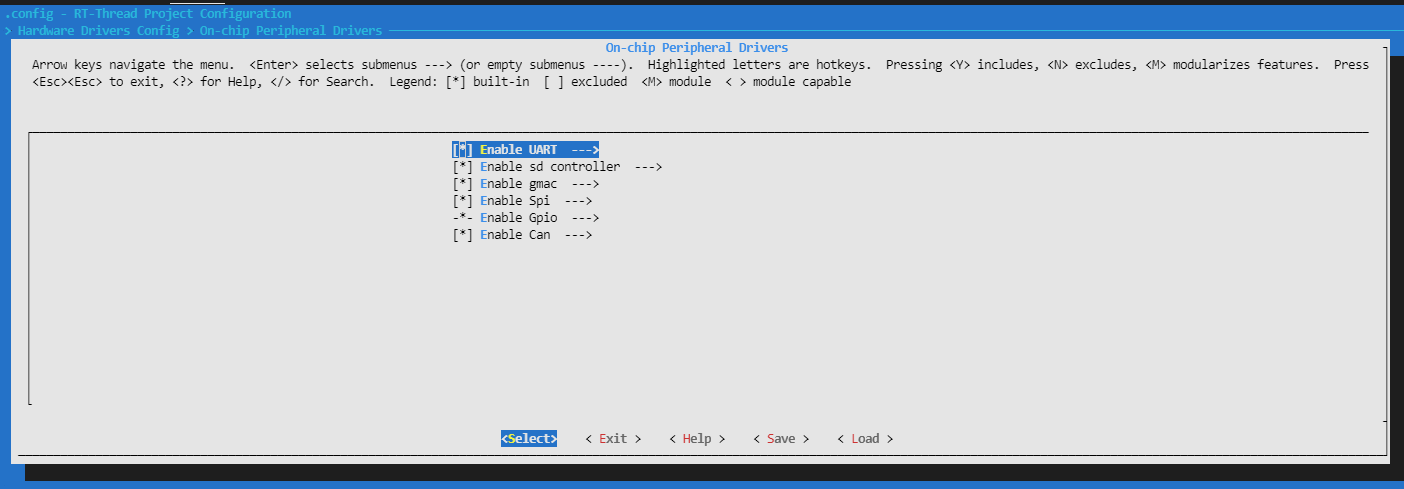

bsp/ft2004/Kconfig

0 → 100644

bsp/ft2004/README.md

0 → 100644

bsp/ft2004/SConscript

0 → 100644

bsp/ft2004/SConstruct

0 → 100644

bsp/ft2004/applications/main.c

0 → 100644

bsp/ft2004/drivers/SConscript

0 → 100644

bsp/ft2004/drivers/board.c

0 → 100644

bsp/ft2004/drivers/board.h

0 → 100644

bsp/ft2004/drivers/drv_can.c

0 → 100644

bsp/ft2004/drivers/drv_can.h

0 → 100644

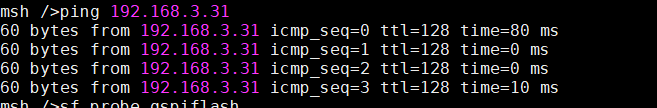

bsp/ft2004/drivers/drv_eth.c

0 → 100644

bsp/ft2004/drivers/drv_eth.h

0 → 100644

bsp/ft2004/drivers/drv_log.h

0 → 100644

bsp/ft2004/drivers/drv_qspi.c

0 → 100644

bsp/ft2004/drivers/drv_qspi.h

0 → 100644

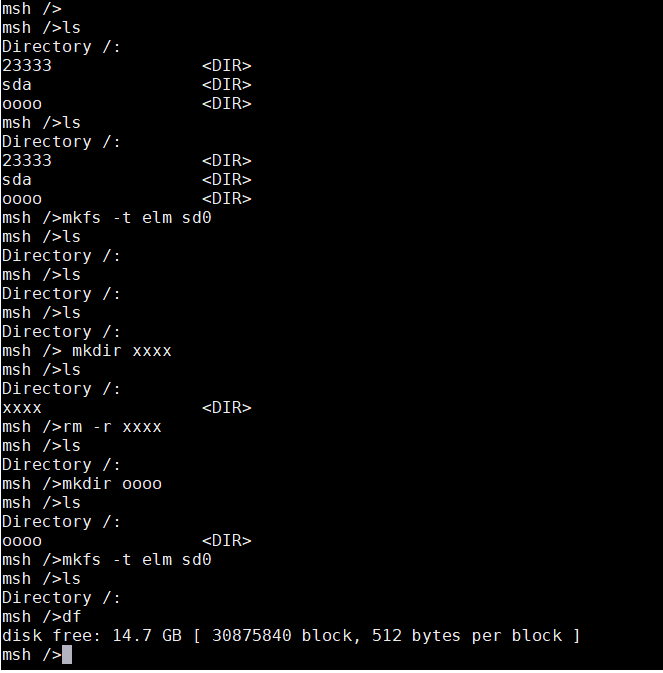

bsp/ft2004/drivers/drv_sdcard.c

0 → 100644

bsp/ft2004/drivers/drv_sdctrl.c

0 → 100644

bsp/ft2004/drivers/drv_sdctrl.h

0 → 100644

bsp/ft2004/drivers/drv_spi.c

0 → 100644

bsp/ft2004/drivers/drv_spi.h

0 → 100644

bsp/ft2004/drivers/drv_usart.c

0 → 100644

bsp/ft2004/drivers/drv_usart.h

0 → 100644

bsp/ft2004/drivers/ft2004.c

0 → 100644

bsp/ft2004/drivers/ft2004.h

0 → 100644

bsp/ft2004/drivers/ft2004_cpu.S

0 → 100644

bsp/ft2004/drivers/serial.h

0 → 100644

21.8 KB

10.7 KB

bsp/ft2004/figures/rttsd调试.png

0 → 100644

21.8 KB

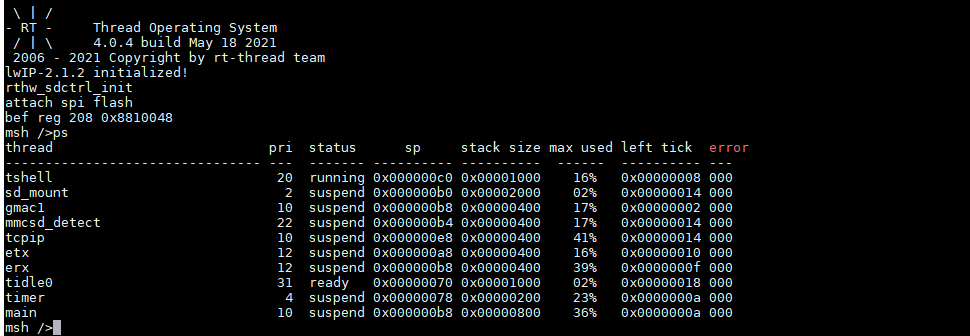

bsp/ft2004/figures/启动演示图.png

0 → 100644

23.9 KB

bsp/ft2004/ft_aarch32.lds

0 → 100644

bsp/ft2004/libraries/.gitignore

0 → 100644

bsp/ft2004/libraries/Kconfig

0 → 100644

此差异已折叠。

bsp/ft2004/libraries/LICENSE

0 → 100644

此差异已折叠。

bsp/ft2004/libraries/SConscript

0 → 100644

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

bsp/ft2004/libraries/readme.md

0 → 100644

此差异已折叠。

bsp/ft2004/make.sh

0 → 100644

此差异已折叠。

bsp/ft2004/rtconfig.h

0 → 100644

此差异已折叠。

bsp/ft2004/rtconfig.py

0 → 100644

此差异已折叠。

bsp/gd32303e-eval/cconfig.h

已删除

100644 → 0

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

bsp/qemu-riscv-virt64/.config

0 → 100644

此差异已折叠。

bsp/qemu-riscv-virt64/Kconfig

0 → 100644

此差异已折叠。

bsp/qemu-riscv-virt64/README.md

0 → 100644

此差异已折叠。

此差异已折叠。

bsp/qemu-riscv-virt64/SConscript

0 → 100644

此差异已折叠。

bsp/qemu-riscv-virt64/SConstruct

0 → 100644

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

bsp/qemu-riscv-virt64/driver/io.h

0 → 100644

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

bsp/qemu-riscv-virt64/link.lds

0 → 100644

此差异已折叠。

此差异已折叠。

bsp/qemu-riscv-virt64/qemu-dbg.sh

0 → 100644

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

bsp/qemu-riscv-virt64/rtconfig.h

0 → 100644

此差异已折叠。

bsp/qemu-riscv-virt64/rtconfig.py

0 → 100644

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

examples/rt-link/rtlink_example.c

0 → 100644

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

libcpu/arm/zynqmp-r5/xil_mmu.h

0 → 100644

此差异已折叠。

libcpu/arm/zynqmp-r5/xil_mpu.c

0 → 100644

此差异已折叠。

libcpu/arm/zynqmp-r5/xil_mpu.h

0 → 100644

此差异已折叠。

libcpu/risc-v/virt64/SConscript

0 → 100644

此差异已折叠。

此差异已折叠。

libcpu/risc-v/virt64/cpuport.c

0 → 100644

此差异已折叠。

libcpu/risc-v/virt64/cpuport.h

0 → 100644

此差异已折叠。

libcpu/risc-v/virt64/interrupt.c

0 → 100644

此差异已折叠。

libcpu/risc-v/virt64/interrupt.h

0 → 100644

此差异已折叠。

此差异已折叠。

libcpu/risc-v/virt64/riscv.h

0 → 100644

此差异已折叠。

libcpu/risc-v/virt64/riscv_io.h

0 → 100644

此差异已折叠。

libcpu/risc-v/virt64/stack.h

0 → 100644

此差异已折叠。

libcpu/risc-v/virt64/stackframe.h

0 → 100644

此差异已折叠。

此差异已折叠。

libcpu/risc-v/virt64/tick.c

0 → 100644

此差异已折叠。

libcpu/risc-v/virt64/tick.h

0 → 100644

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。