Merge pull request #4910 from Ouxiaolong/master

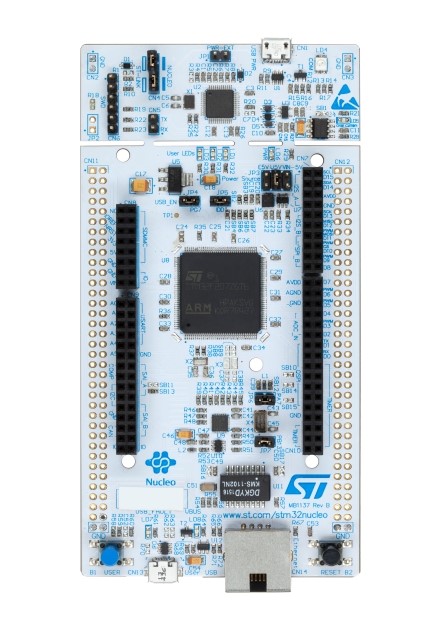

add stm32f746-st-nucleo

Showing

此差异已折叠。

72.2 KB

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

add stm32f746-st-nucleo

72.2 KB