Merge pull request #2336 from Guozhanxin/rtt_sensor

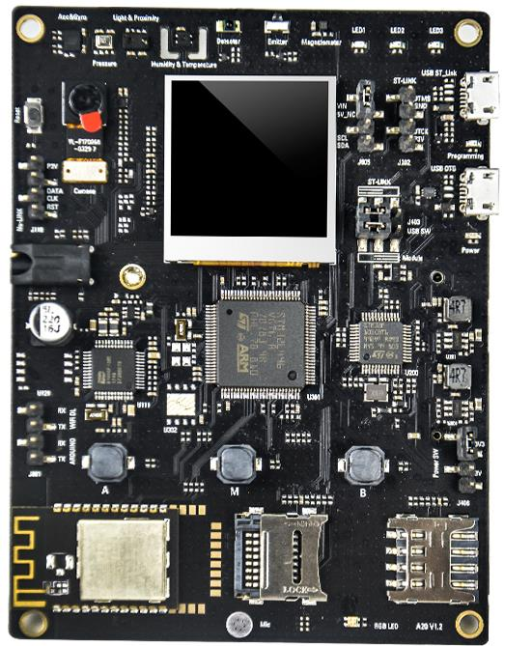

添加 阿里 DeveloperKit 开发板

Showing

此差异已折叠。

此差异已折叠。

712.8 KB

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

添加 阿里 DeveloperKit 开发板

712.8 KB