Merge pull request #3153 from qgyhd1234/h7_tool

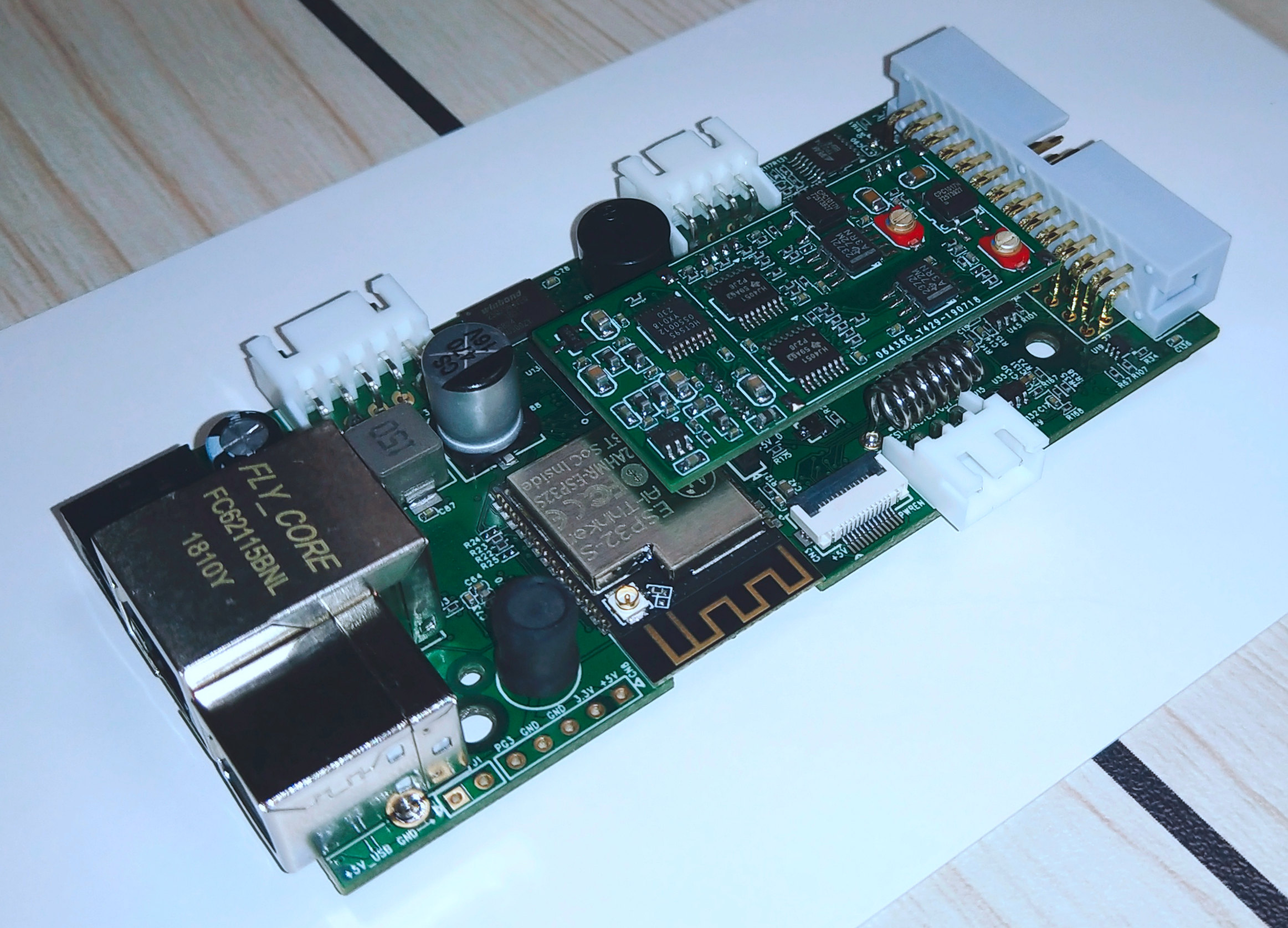

【添加】添加 H7-TOOL bsp

Showing

此差异已折叠。

此差异已折叠。

626.4 KB

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

【添加】添加 H7-TOOL bsp

626.4 KB