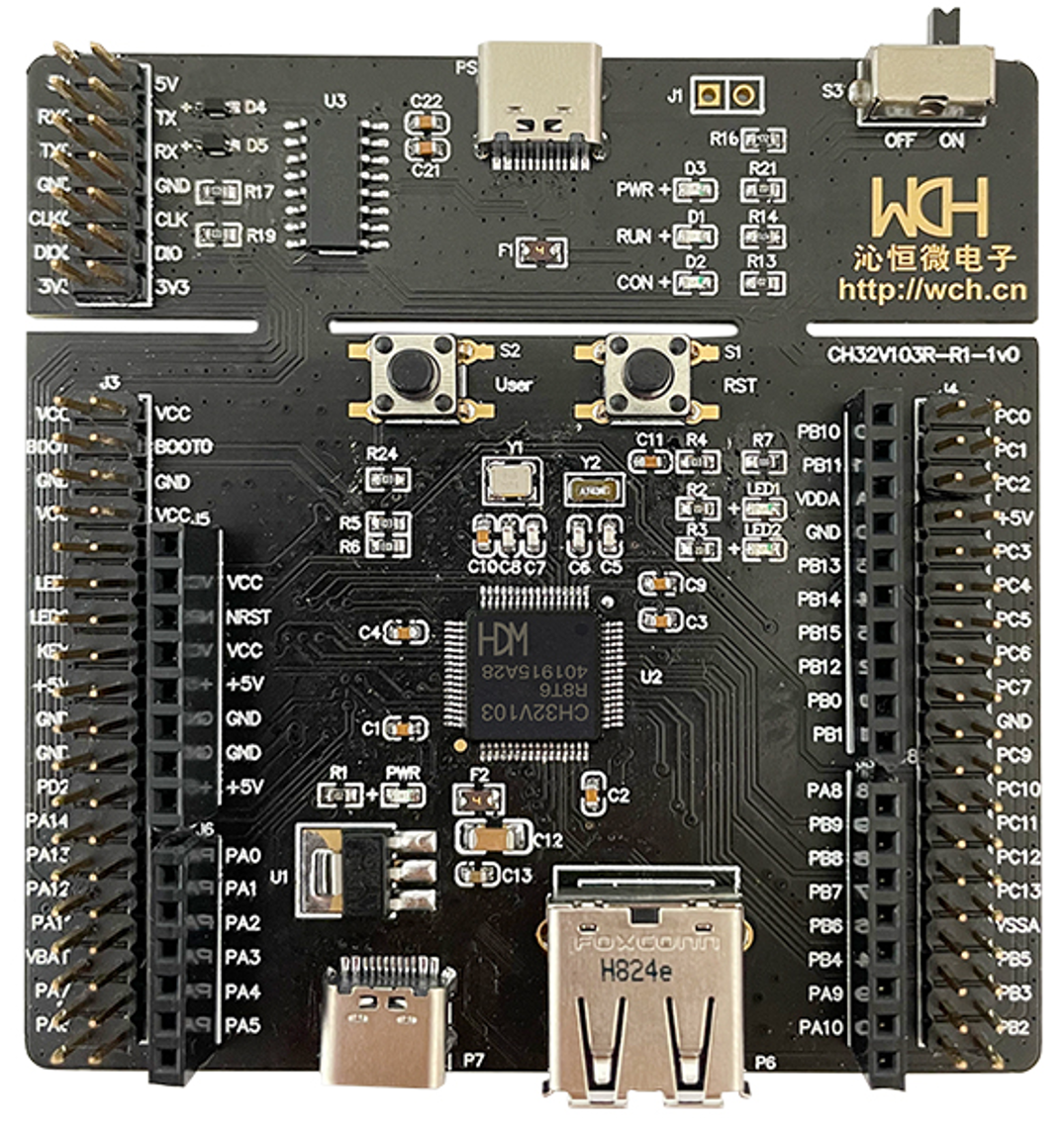

[bsp/ch32v103r-evt] add ch32v103r-evt bsp

feat: move MRS demo source to bsp and libraries folder feat: update Sconscript feat: modify SConstruct in the bsp feat: use the rtconfig.py of gd32vf103v-eval bsp to modify feat: use the MRS's rtconfig.h temoporarily feat: update Kconfig files feat: use the MRS's .ld and rename as link.lds feat: add ch32v1 porting folder perf: remove board/system_ch32v10x.c fix: define SOC_ARM_SERIES_CH32V103 in rtconfig.h fix: add some neccessary macros in rtconfig.h perf: use the menuconfig to generate rtconfig.h feat: add readme.md fix: correct the bad encode in main.c fix: include board.h in main.c perf: check and update README.md perf: remove ch32f10x_port_cn.md feat: ignore the standard libraries's CI checking feat: add sdk_dist.py fix: correct some style errors again perf: simply the board/kconfig fix: format ch32v103r-evt fix: format drvs and libcpu

Showing

bsp/wch/risc-v/.ignore_format.yml

0 → 100644

因为 它太大了无法显示 source diff 。你可以改为 查看blob。

因为 它太大了无法显示 source diff 。你可以改为 查看blob。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

bsp/wch/risc-v/Libraries/Kconfig

0 → 100644

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

3.5 MB

327.4 KB

此差异已折叠。

此差异已折叠。

bsp/wch/risc-v/tools/sdk_dist.py

0 → 100644

此差异已折叠。

libcpu/risc-v/ch32v1/SConscript

0 → 100644

此差异已折叠。

此差异已折叠。

libcpu/risc-v/ch32v1/cpuport.c

0 → 100644

此差异已折叠。

libcpu/risc-v/ch32v1/cpuport.h

0 → 100644

此差异已折叠。

此差异已折叠。