中断是如何管理的? CPU之间又是如何通讯的?

搜索 @note_pic 方便理解画的字符图 搜索 @note_why 尚未看明白的地方,如果您看明白了,请告知完善 搜索 @note_thinking 一点思考和吐槽的地方 搜索 @note_#if0 由第三方项目提供不由内核源码中定义的极为重要的结构体,为方便理解而添加的 搜索 @note_good 给源码点赞

Showing

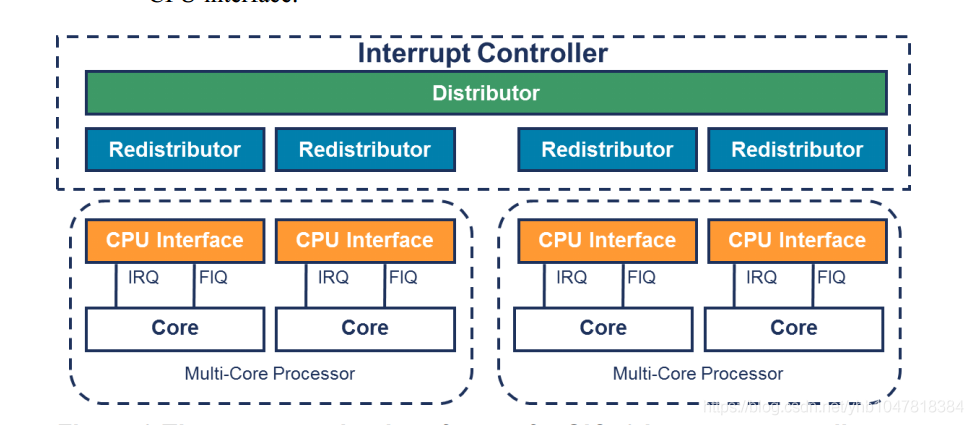

zzz/pic/turing/gic_v3.png

0 → 100644

103.7 KB

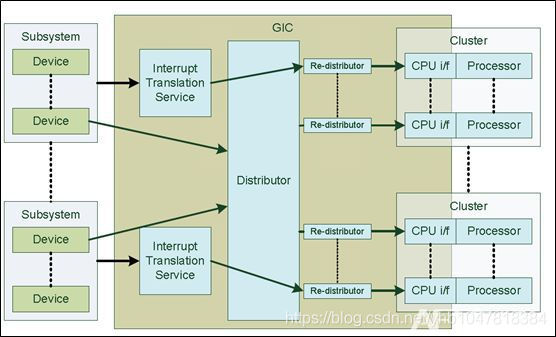

zzz/pic/turing/中断处理流程.jpeg

0 → 100644

34.3 KB

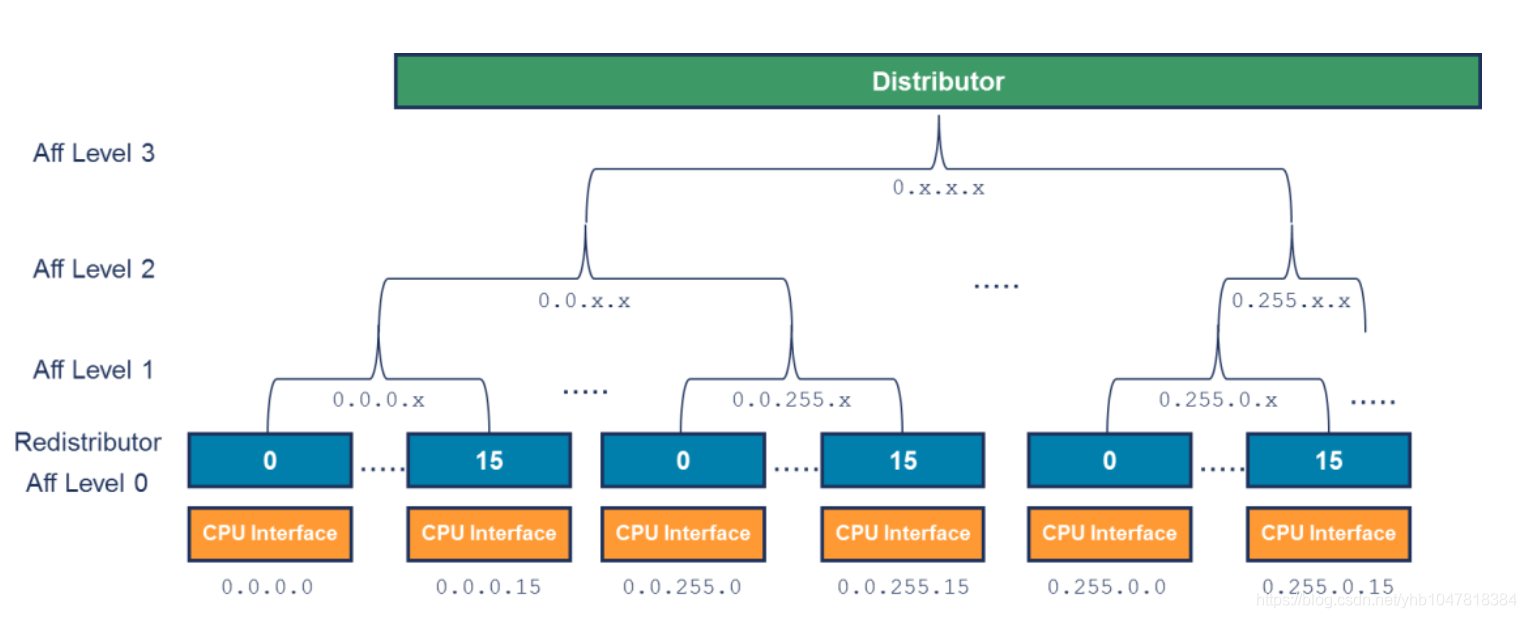

zzz/pic/turing/中断路由.png

0 → 100644

129.3 KB