!372 [本次提交内容:在TI公司C6000...

!372 [本次提交内容:在TI公司C6000 DSP处理器上成功移植rt-thread操作系统;主要在libcpu/ti-dsp/c6x添加keystone架构底层代码,在bsp/ti-c6678添加bsp工程,该工程已在本人的开发板上成功运行] Merge pull request !372 from hdwei/hdwei

Showing

bsp/ti-tms320c6678/.ccsproject

0 → 100644

bsp/ti-tms320c6678/.cproject

0 → 100644

此差异已折叠。

bsp/ti-tms320c6678/.project

0 → 100644

bsp/ti-tms320c6678/KeyStone.cmd

0 → 100644

bsp/ti-tms320c6678/README.md

0 → 100644

24.9 KB

55.3 KB

12.6 KB

20.6 KB

36.3 KB

25.2 KB

60.4 KB

bsp/ti-tms320c6678/rtconfig.h

0 → 100644

libcpu/ti-dsp/c6x/SConscript

0 → 100644

libcpu/ti-dsp/c6x/c66xx.h

0 → 100644

libcpu/ti-dsp/c6x/context.asm

0 → 100644

libcpu/ti-dsp/c6x/contextinc.asm

0 → 100644

libcpu/ti-dsp/c6x/cpuport.c

0 → 100644

libcpu/ti-dsp/c6x/interrupt.c

0 → 100644

libcpu/ti-dsp/c6x/interrupt.h

0 → 100644

libcpu/ti-dsp/c6x/intexc.asm

0 → 100644

libcpu/ti-dsp/c6x/stack.c

0 → 100644

libcpu/ti-dsp/c6x/trap.c

0 → 100644

libcpu/ti-dsp/c6x/trap.h

0 → 100644

libcpu/ti-dsp/c6x/vector.asm

0 → 100644

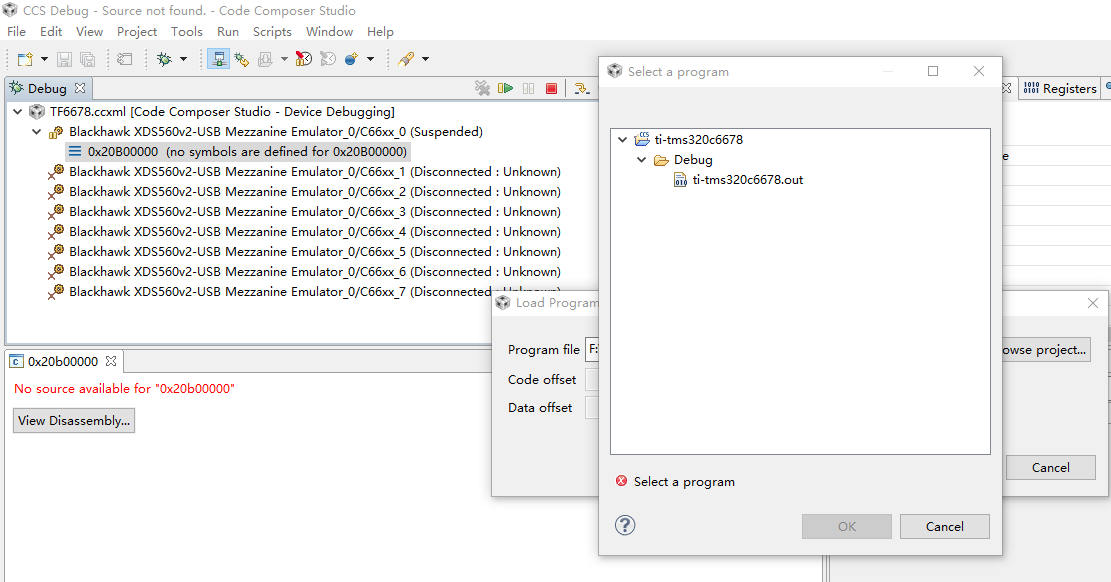

.png)

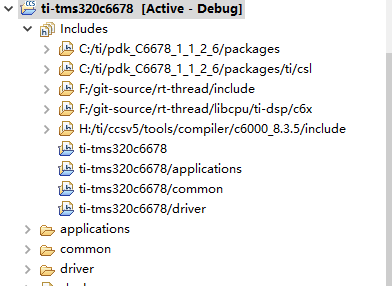

.png)

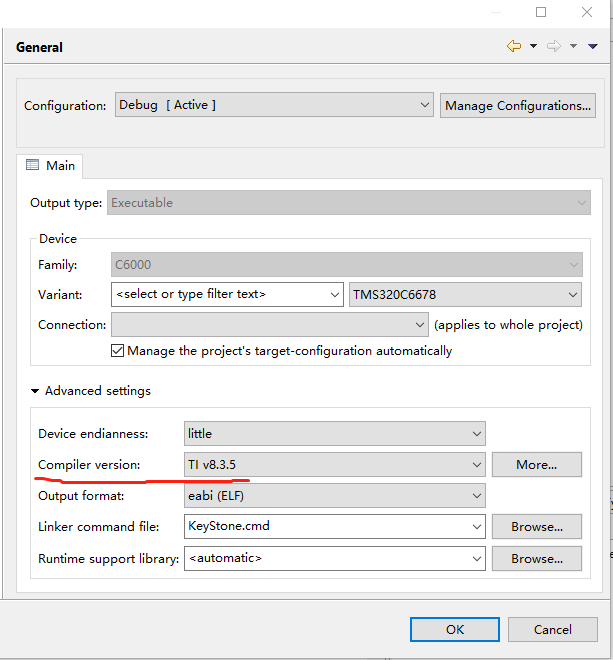

.png)

.png)