Merge pull request #2088 from RT-Thread/bsp_k210

[libcpu] Add k210 BSP.

Showing

bsp/k210/.config

0 → 100644

bsp/k210/Kconfig

0 → 100644

bsp/k210/README.md

0 → 100644

bsp/k210/SConscript

0 → 100644

bsp/k210/SConstruct

0 → 100644

bsp/k210/applications/SConscript

0 → 100644

bsp/k210/applications/main.c

0 → 100644

bsp/k210/applications/mnt.c

0 → 100644

bsp/k210/driver/Kconfig

0 → 100644

bsp/k210/driver/SConscript

0 → 100644

bsp/k210/driver/board.c

0 → 100644

bsp/k210/driver/board.h

0 → 100644

bsp/k210/driver/drv_uart.c

0 → 100644

bsp/k210/driver/drv_uart.h

0 → 100644

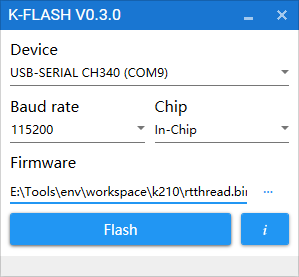

bsp/k210/images/flash.png

0 → 100644

7.4 KB

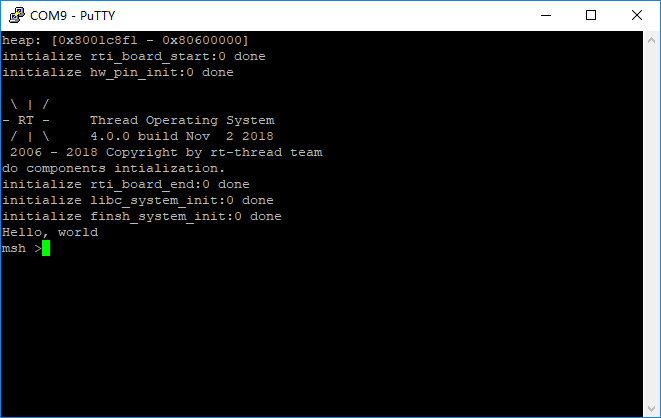

bsp/k210/images/k210.png

0 → 100644

7.3 KB

bsp/k210/link.lds

0 → 100644

bsp/k210/link_stacksize.lds

0 → 100644

bsp/k210/rtconfig.h

0 → 100644

bsp/k210/rtconfig.py

0 → 100644

libcpu/risc-v/k210/interrupt.c

0 → 100644

libcpu/risc-v/k210/startup_gcc.S

0 → 100644

libcpu/risc-v/k210/tick.c

0 → 100644

libcpu/risc-v/k210/tick.h

0 → 100644