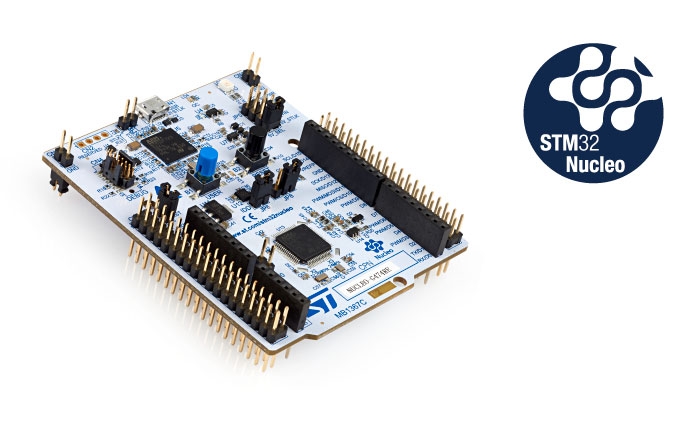

add stm32g474-st-nucleo bsp (#5362)

* add stm32g474-st-nucleo bsp * format * format

Showing

122.3 KB

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

* add stm32g474-st-nucleo bsp * format * format

122.3 KB