Merge pull request #5 from RT-Thread/master

pr

Showing

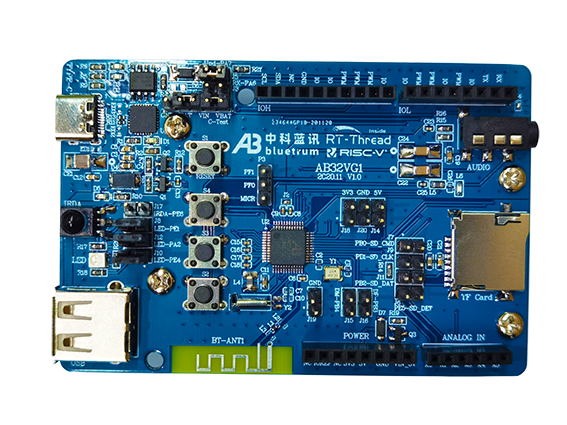

bsp/bluetrum/README.md

0 → 100644

此差异已折叠。

文件已添加

943.3 KB

文件已添加

文件已添加

bsp/bluetrum/libcpu/cpu/cpuport.c

0 → 100644

bsp/bluetrum/tools/sdk_dist.py

0 → 100644

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。