1.Modify project directory structure

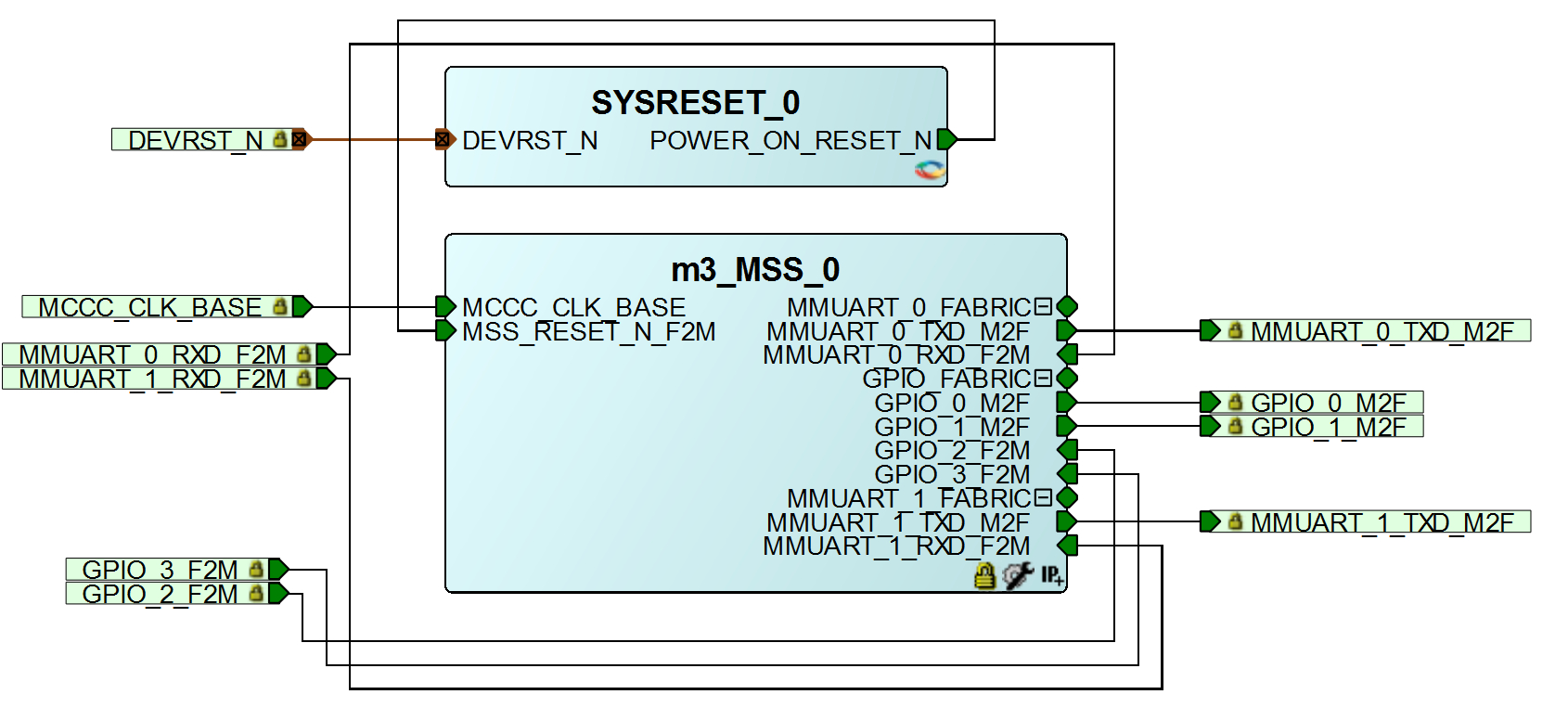

2.Add support for GPIO and UART peripherals 3.Add pin and serial device driver support 4.Put pictures in local folder 5.Modify README file

Showing

文件已移动

文件已移动

文件已移动

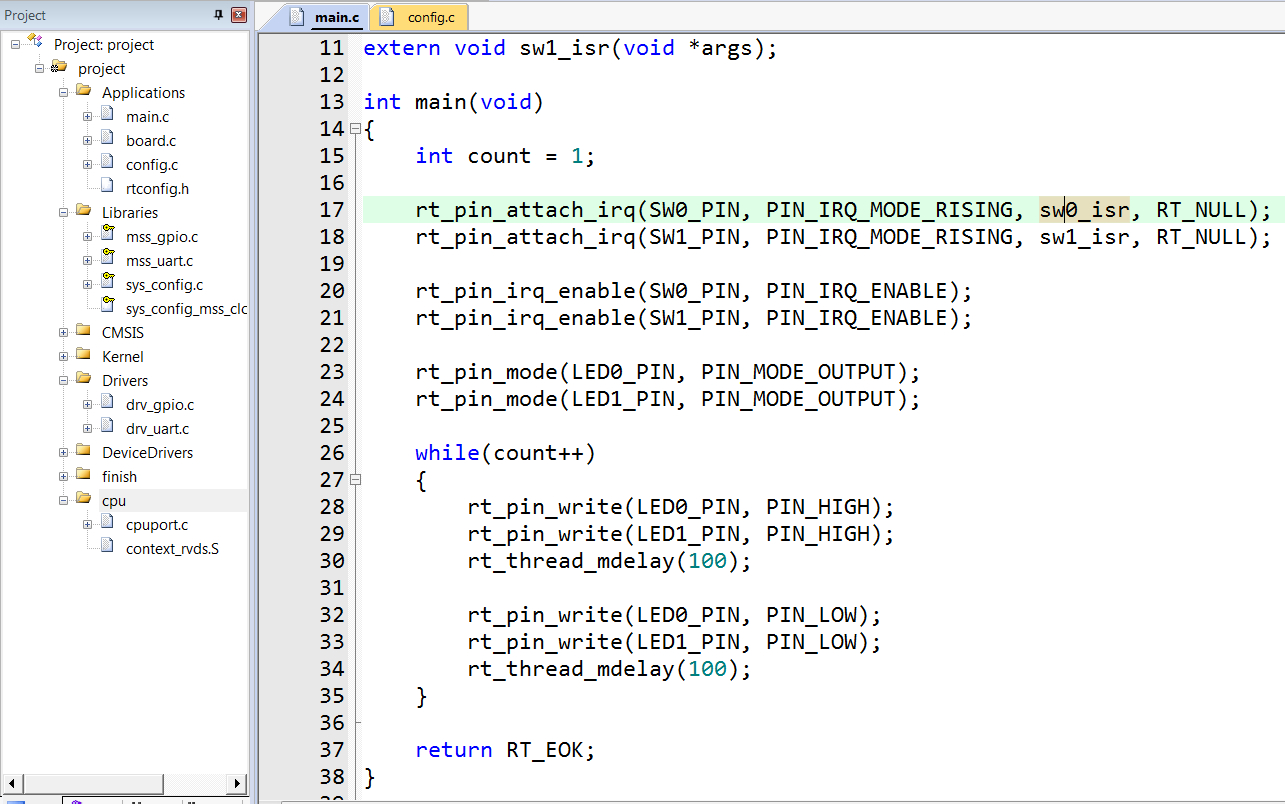

bsp/smartfusion2/board/config.c

0 → 100644

1006.8 KB

581.0 KB

157.8 KB

154.4 KB

151.7 KB

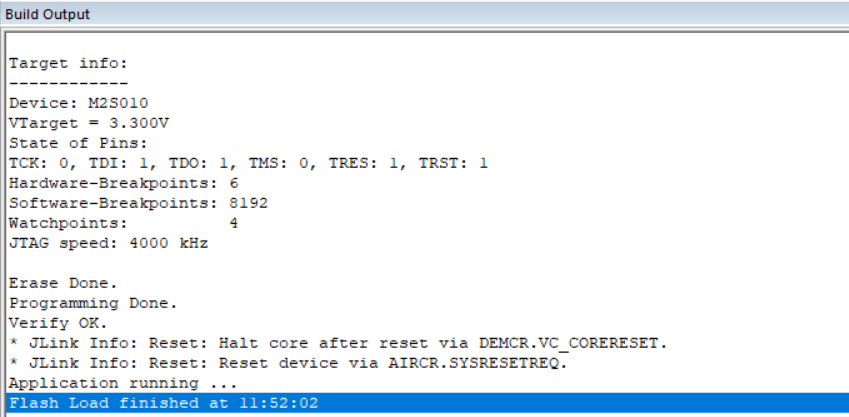

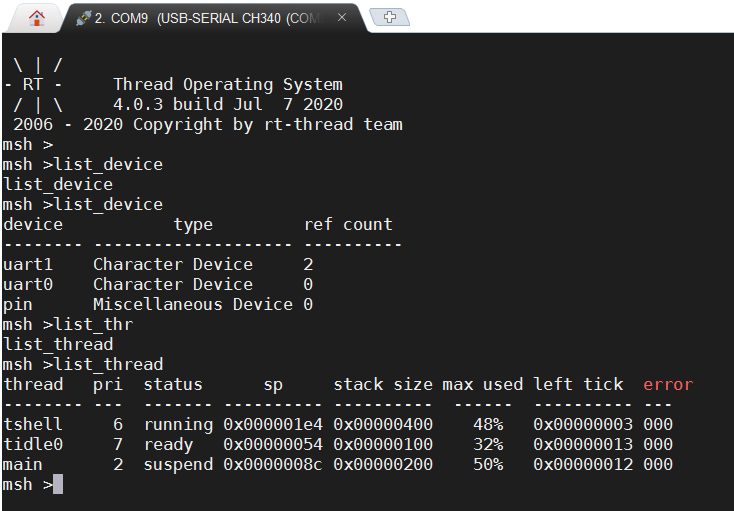

bsp/smartfusion2/figures/log.jpg

0 → 100644

259.7 KB

491.9 KB

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

bsp/smartfusion2/rtconfig.h

0 → 100644

bsp/smartfusion2/rtconfig.py

0 → 100644

此差异已折叠。

bsp/smartfusion2/user/main.c

已删除

100644 → 0

此差异已折叠。

此差异已折叠。