Merge pull request #5262 from ShermanShao/master

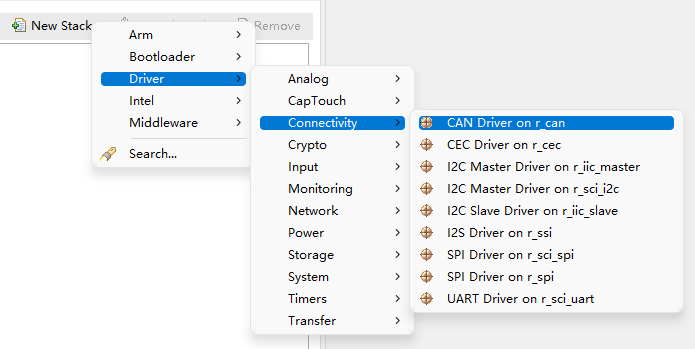

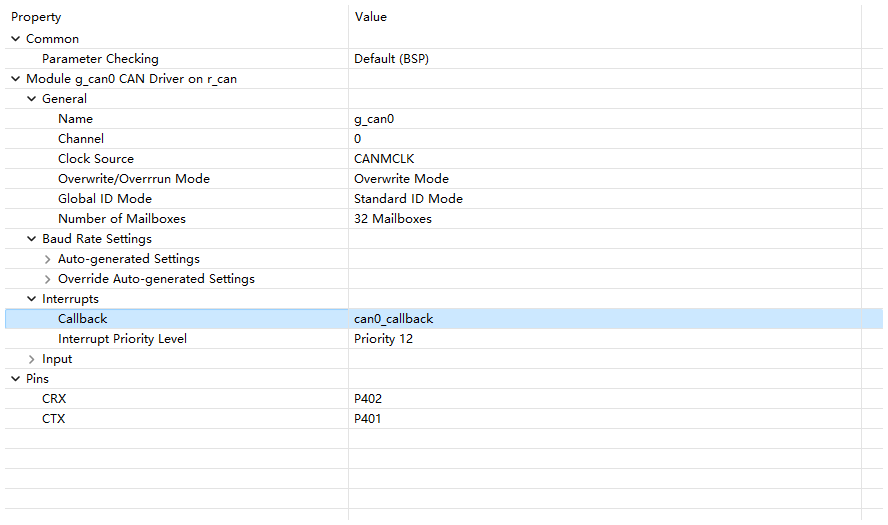

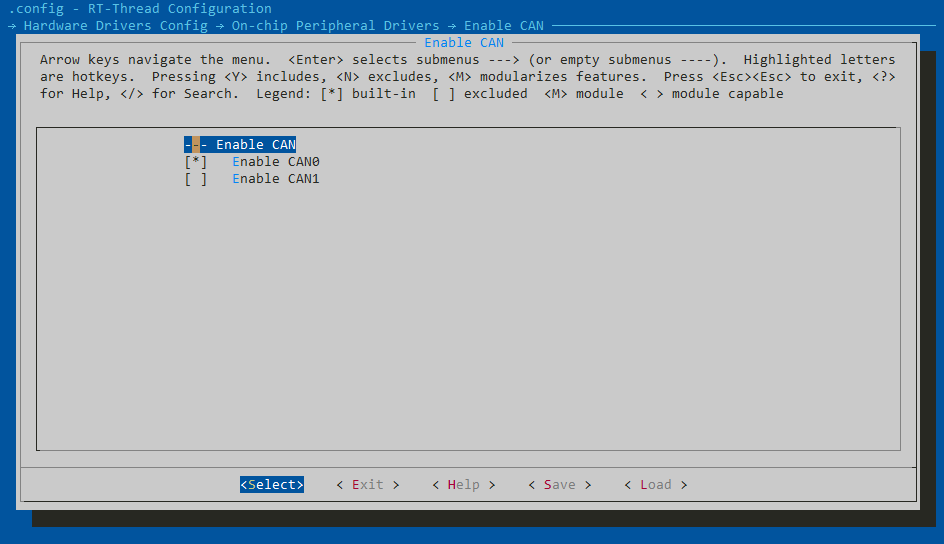

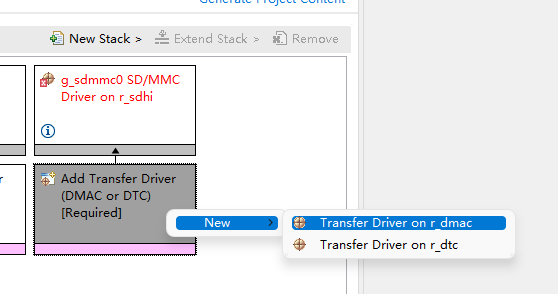

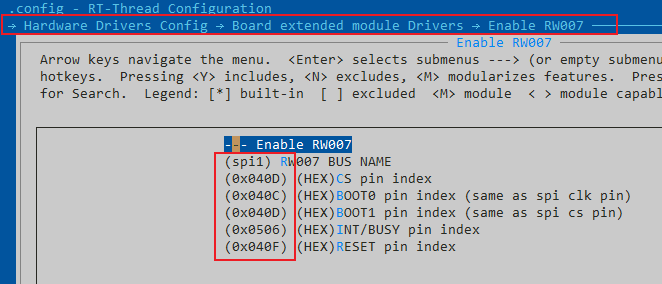

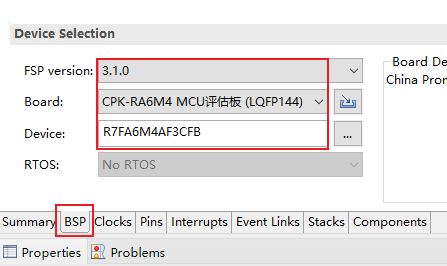

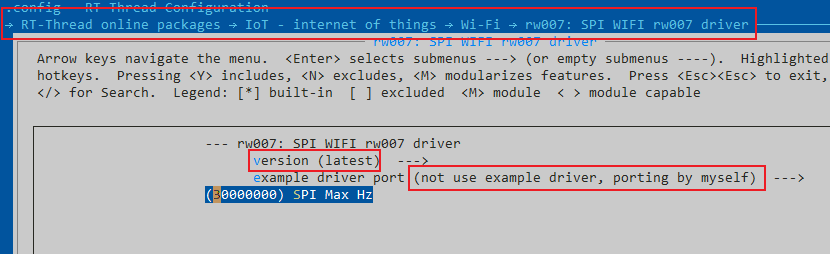

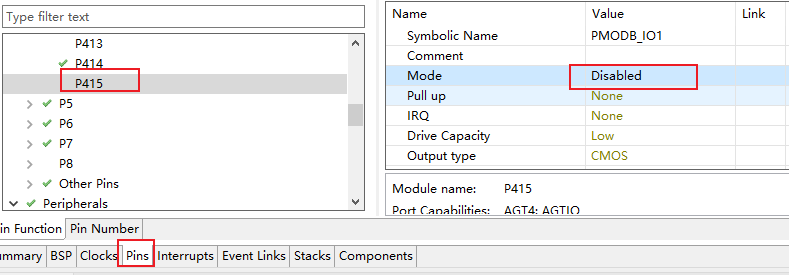

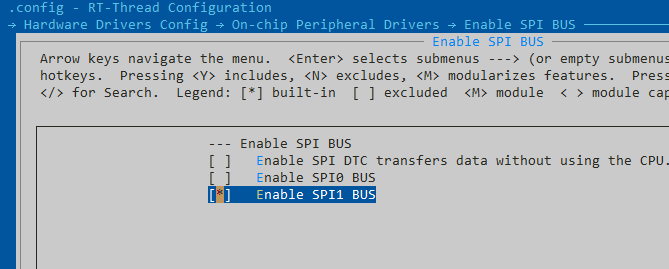

[BSP/RA6M4-CPK] 添加 CAN、RW007 的支持

Showing

bsp/ra6m4-cpk/.gitignore

0 → 100644

27.8 KB

21.1 KB

22.2 KB

17.4 KB

31.4 KB

25.2 KB

13.4 KB

19.0 KB

16.2 KB

26.0 KB

11.5 KB

20.7 KB

17.8 KB

20.4 KB

19.5 KB

17.6 KB

39.7 KB

29.6 KB

11.2 KB

17.5 KB

31.9 KB

29.9 KB

28.2 KB

25.8 KB

bsp/ra6m4-cpk/drivers/drv_can.c

0 → 100644

bsp/ra6m4-cpk/drivers/drv_can.h

0 → 100644