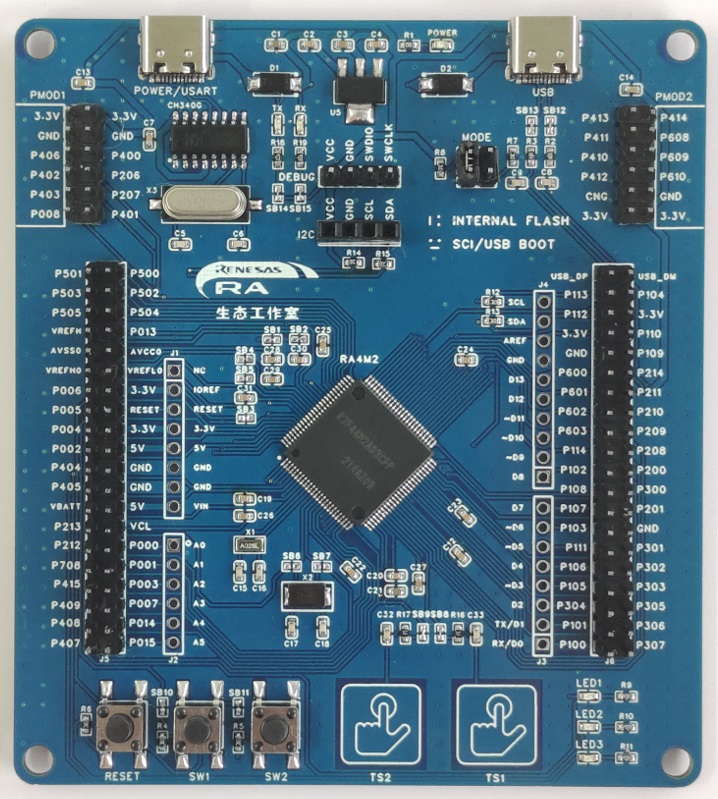

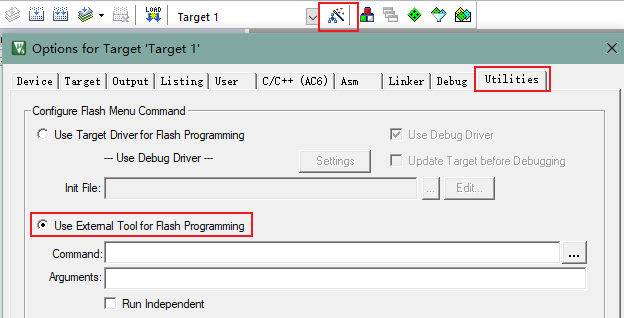

add ra4m2 soc support, add sci spi support for ra4m2 (#6707)

* add ra4m2 soc support, add sci spi support for ra4m2 * update ra4m2-eco/README.md * update ra4m2-eco/README.md * rename board picture name. * reduce picture size, update README.md, remove file 'Target 1.bat' * reduce picture size

Showing

bsp/renesas/ra4m2-eco/.api_xml

0 → 100644

bsp/renesas/ra4m2-eco/.config

0 → 100644

此差异已折叠。

bsp/renesas/ra4m2-eco/.gitignore

0 → 100644

bsp/renesas/ra4m2-eco/.secure_xml

0 → 100644

bsp/renesas/ra4m2-eco/Kconfig

0 → 100644

bsp/renesas/ra4m2-eco/README.md

0 → 100644

bsp/renesas/ra4m2-eco/SConscript

0 → 100644

bsp/renesas/ra4m2-eco/SConstruct

0 → 100644

此差异已折叠。

252.7 KB

19.0 KB

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

bsp/renesas/ra4m2-eco/rtconfig.h

0 → 100644

此差异已折叠。

bsp/renesas/ra4m2-eco/rtconfig.py

0 → 100644

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。

此差异已折叠。