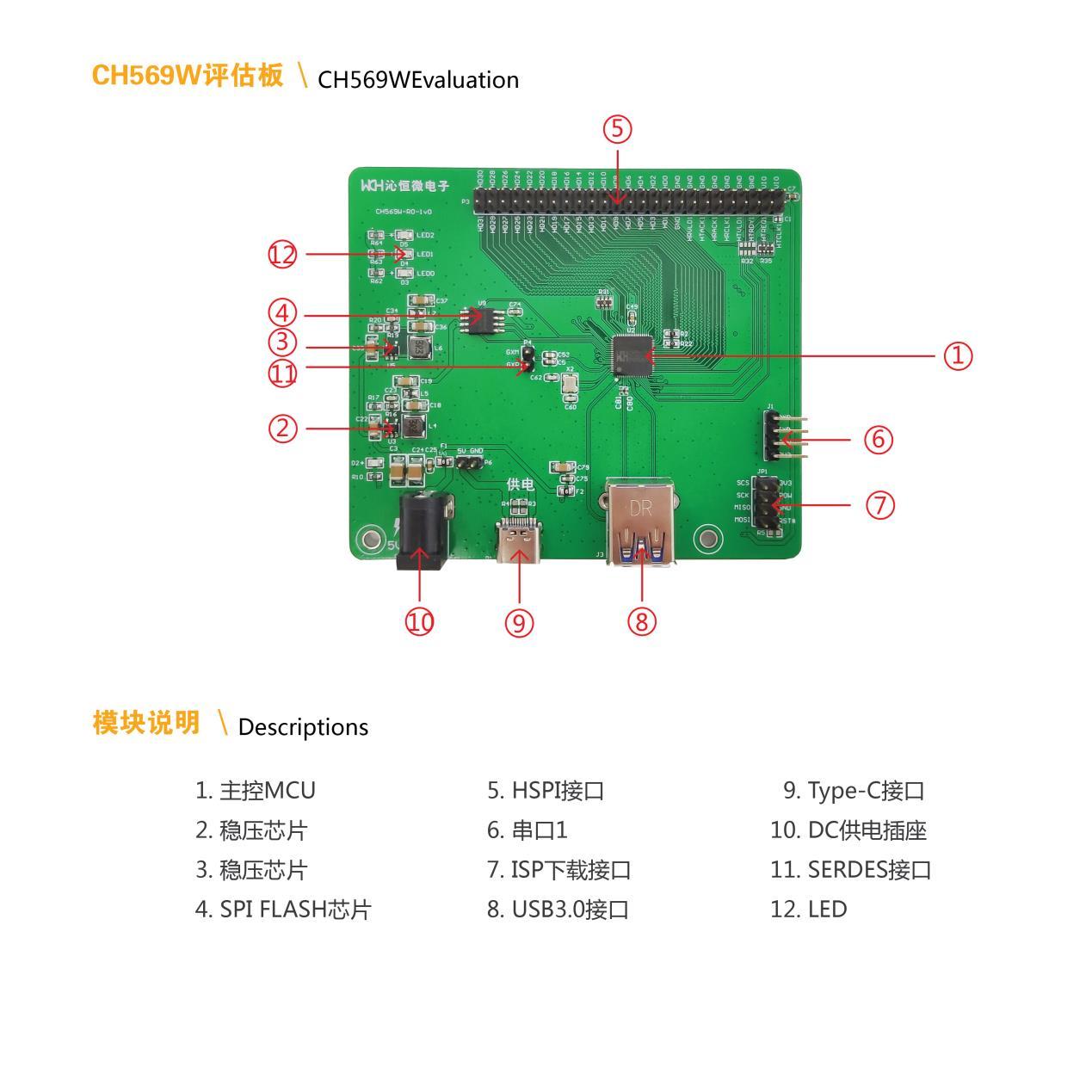

WCH CH569W-R0-1v0 evt board bsp port, first version (#6167)

WCH CH569W-R0-1v0 evt board bsp port, first version dev/test under Ubuntu 20.04 toolchain from MounRiver_Studio_Community_Linux_x64_V120 tested drivers : SysTick, gpio, gpio interrupt, uart1 (RX interrupt, TX polling) libcpu/risc-v/SConscript : group includes rtconfig.CPU only if folder exists libcpu/risc-v/common/cpuport.c/rt_hw_context_switch_interrupt() : make it RT_WEAK for customization

Showing

bsp/wch/risc-v/ch569w-evt/.config

0 → 100644

bsp/wch/risc-v/ch569w-evt/Kconfig

0 → 100644

112.2 KB